### Section 10

### **Computer Arithmetic**

Slides with white background courtesy of Mano text for this class

### **Digital Hardware Algorithms**

- Arithmetic operations

- Addition, subtraction, multiplication, division

- Data types

- Fixed-point binary

Signed-magnitude representation

Signed-2's complement representation

- Floating-point binary

- Binary-coded decimal (BCD)

|             | Add        | Subtract Magnitudes |              |              |  |

|-------------|------------|---------------------|--------------|--------------|--|

| Operation   | Magnitudes | When $A > B$        | When $A < B$ | When $A = 1$ |  |

| (+A) + (+B) | +(A + B)   |                     |              |              |  |

| (+A) + (-B) |            | +(A - B)            | -(B-A)       | +(A - B)     |  |

| (-A) + (+B) |            | -(A - B)            | +(B-A)       | +(A - B)     |  |

| (-A) + (-B) | -(A + B)   |                     |              |              |  |

| (+A) - (+B) |            | +(A - B)            | -(B-A)       | +(A - B)     |  |

| (+A) - (-B) | +(A + B)   |                     |              |              |  |

| (-A) - (+B) | -(A + B)   |                     |              |              |  |

| (-A) - (-B) |            | -(A - B)            | +(B-A)       | +(A - B)     |  |

|             |            |                     |              |              |  |

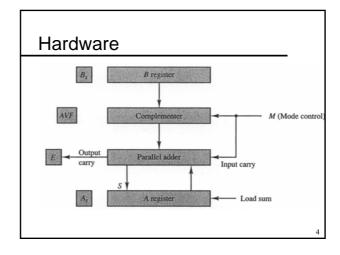

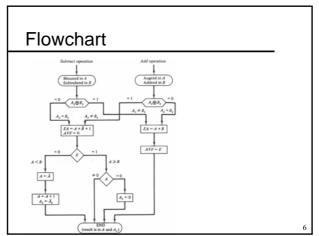

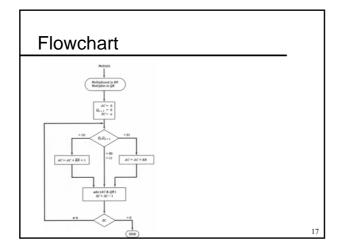

## Description• $A_s$ Sign of A• $B_s$ Sign of B• $A_s \& A$ Accumulator• AVFOverflow bit for A + B• EOutput carry for parallel adder

© 2004 by Ted Borys. All rights reserved.

Г

14

٦

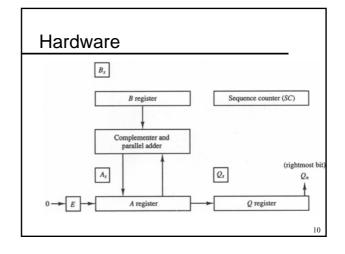

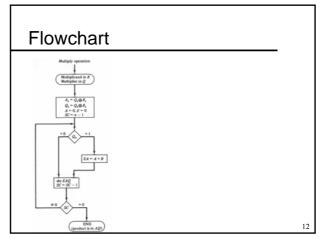

| Multiplicand $B = 10111$           | Е | Α     | Q     | SC |

|------------------------------------|---|-------|-------|----|

| Multiplier in $Q$                  | 0 | 00000 | 10011 | 10 |

| $Q_n = 1$ ; add B                  |   | 10111 |       |    |

| First partial product              | 0 | 10111 |       |    |

| Shift right EAQ                    | 0 | 01011 | 11001 | 10 |

| $Q_n = 1$ ; add B                  |   | 10111 |       |    |

| Second partial product             | 1 | 00010 |       |    |

| Shift right EAQ                    | 0 | 10001 | 01100 | 01 |

| $Q_n = 0$ ; shift right EAQ        | 0 | 01000 | 10110 | 01 |

| $Q_n = 0$ ; shift right EAQ        | 0 | 00100 | 01011 | 00 |

| $Q_n = 1$ ; add B                  |   | 10111 |       |    |

| Fifth partial product              | 0 | 11011 |       |    |

| Shift right EAQ                    | 0 | 01101 | 10101 | 00 |

| Final product in $AQ = 0110110101$ |   |       |       |    |

|                                    |   |       |       |    |

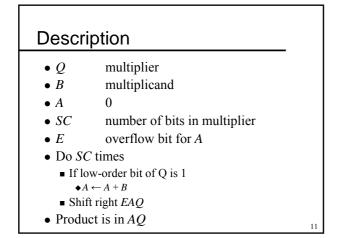

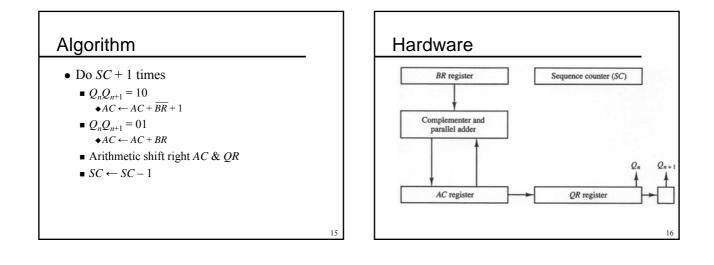

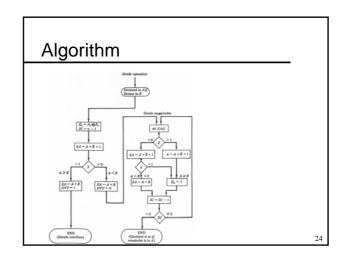

### Multiply Signed-2's Complement

- Booth algorithm

- QR multiplier

- $Q_n$  least significant bit of QR

- $Q_{n+1}$  previous least significant bit of QR

- BR multiplicand

- *AC* 0

- *SC* number of bits in multiplier

|      |      | BR = 10111                  |       |       |           |     |

|------|------|-----------------------------|-------|-------|-----------|-----|

| Qn Q | 2n+1 | $\overline{BR}$ + 1 = 01001 | AC    | QR    | $Q_{n+1}$ | SC  |

|      |      | Initial                     | 00000 | 10011 | 0         | 101 |

| 1    | 0    | Subtract BR                 | 01001 |       |           |     |

|      |      |                             | 01001 |       |           |     |

|      |      | ashr                        | 00100 | 11001 | 1         | 100 |

| 1    | 1    | ashr                        | 00010 | 01100 | 1         | 011 |

| 0    | 1    | Add BR                      | 10111 |       |           |     |

|      |      | 11001                       |       |       |           |     |

|      |      | ashr                        | 11100 | 10110 | 0         | 010 |

| 0    | 0    | ashr                        | 11110 | 01011 | 0         | 001 |

| 1    | 0    | Subtract BR                 | 01001 |       |           |     |

|      |      |                             | 00111 |       |           |     |

|      |      | ashr                        | 00011 | 10101 | 1         | 000 |

© 2004 by Ted Borys. All rights reserved.

19

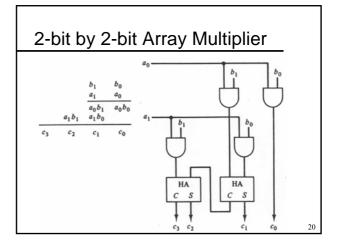

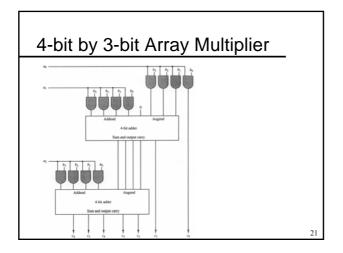

### Array Multiplier

- Combination circuit

- Product generated in one microoperation

- Requires large number of gates

- Became feasible after integrated circuits developed

- Needed for *j* multiplier and *k* multiplicand bits *j* x *k* AND gates

- j 1 *k*-bit adders to produce product of j + k bits

### Divide Fixed-Point Signed-Mag Series of successive compare, shift, and subtract operations

| Divisor:  | 11010       | Quotient = $Q$                                |

|-----------|-------------|-----------------------------------------------|

| B = 10001 | )0111000000 | Dividend = $A$                                |

|           | 01110       | 5 bits of $A < B$ , quotient has 5 bits       |

|           | 011100      | 6 bits of $A \ge B$                           |

|           | -10001      | Shift right $B$ and subtract; enter 1 in $Q$  |

|           | -010110     | 7 bits of remainder $\geq B$                  |

|           | 10001       | Shift right $B$ and subtract; enter 1 in $Q$  |

|           | 001010      | Remainder $< B$ ; enter 0 in Q; shift right B |

|           | 010100      | Remainder $\geq B$                            |

|           | 10001       | Shift right $B$ and subtract; enter 1 in $Q$  |

|           | 000110      | Remainder $< B$ ; enter 0 in Q                |

|           | 00110       | Final remainder                               |

| Examp                                                               | ole:        | 448                              | 3/*            | 17 | = 26 r 6                                             |

|---------------------------------------------------------------------|-------------|----------------------------------|----------------|----|------------------------------------------------------|

| Divisor <i>B</i> = 10001,                                           |             | <u>B</u> + 1 = 01111             |                |    |                                                      |

|                                                                     | E           | 4                                | 0              | SC | Initially,                                           |

| Dividend:<br>shl $EAQ$<br>add $\overline{B} + 1$                    | 0           | 01110<br>11100<br>01111          | 00000          | 5  | AQ dividend                                          |

| E = 1<br>Set $Q_n = 1$<br>shi $EAQ$<br>Add $B + 1$                  | 1<br>0      | 01011<br>01011<br>10110<br>01111 | 00001<br>00010 | •  | <i>B</i> divisor                                     |

| E = 1<br>Set $Q_n = 1$<br>shi $EAQ$<br>Add B + 1                    | 1<br>1<br>0 | 00101<br>00101<br>01010<br>01111 | 00011<br>00110 | 3  | <b>A</b> t = = <b>1</b> = <b>C</b> = = = = = t = = = |

| $E = 0$ ; leave $Q_{a} = 0$<br>Add B                                | 0           | 11001                            | 00110          |    | At end of operation                                  |

| Restore remainder<br>shl EAQ<br>Add B + 1                           | 0           | 01010 10100 01111                | 01100          | 2  | Q quotient                                           |

| E = 1<br>Set $Q_n = 1$<br>sh1 $EAQ$<br>Add $B + 1$                  | 1<br>0      | 00011<br>00011<br>00110<br>01111 | 01101<br>11010 | 1  | A remainder<br>DVF divide overfl                     |

| $E = 0$ ; leave $Q_n = 0$<br>Add B                                  | ō           | 10101                            | 11010          |    | DVF divide overn                                     |

| Restore remainder<br>Neglect E<br>Remainder in A:<br>Quotient in Q: | 1           | 00110                            | 11010          | 0  |                                                      |

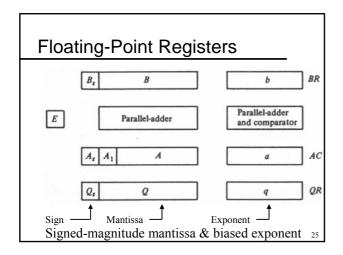

### **Biased Exponent**

- Example

- Real exponent range is -50 to +49

- Add bias of 50 for new range of 0 to 99

- Biased exponent is always a positive number

Easier to deal with

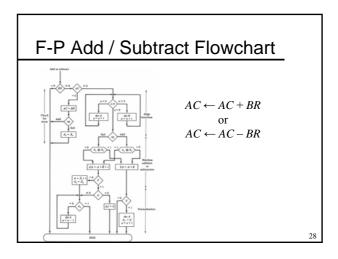

### Floating-Point Add / Subtract

- Check for zeros

- Align the mantissas

- Add or subtract the mantissas

- Normalize the result

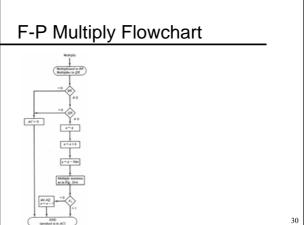

## Floating-Point Multiply F-P Multiply • Check for zeros • Add the exponents • Multiply the mantissas • Normalize the product

© 2004 by Ted Borys. All rights reserved.

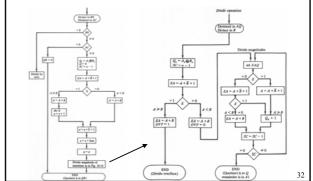

### **Floating-Point Division**

- Check for zeros

- Initialize registers and evaluate the sign

- Align the dividend

- Subtract the exponents

- Divide the mantissas

F-P Division Flowchart

37

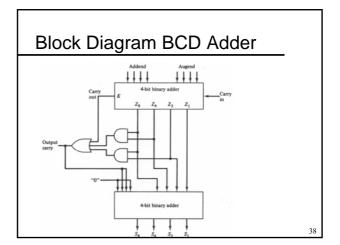

### **BCD** Adder

- Output can't exceed 9 + 9 + 1 = 19

- If binary sum in BCD digit > 1001, add 0110

- Given

- Output of binary adder is  $Z_8 Z_4 Z_2 Z_1$

- Output carry K

- BCD output carry  $C = K + Z_8 Z_4 + Z_8 Z_2$

| Exam                  | ples                                                                                            |                                                                                                                                     |                                                                                                                            |

|-----------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| • 9<br><u>7</u><br>16 | $ \begin{array}{r} 1001 \\ \underline{0111} \\ 1 0000 \\ \underline{0110} \\ 0110 \end{array} $ | $\begin{array}{rrrr} 9 & 1001 \\ \underline{9} & \underline{1001} \\ 18 & 1 & 0010 \\ & & \underline{0110} \\ & & 1000 \end{array}$ | $\begin{array}{c} 6 & 0110 \\ \underline{4} & \underline{0100} \\ 10 & 1010 \\ & \underline{0110} \\ 1 & 0000 \end{array}$ |

|                       |                                                                                                 |                                                                                                                                     | 39                                                                                                                         |

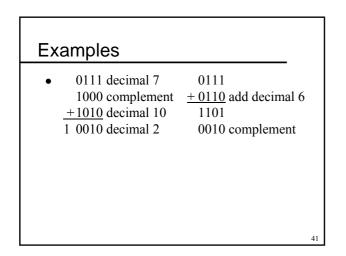

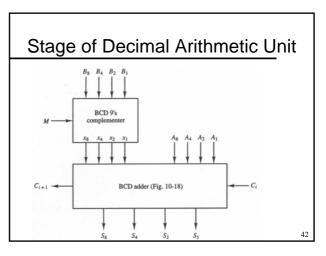

# BCD Subtraction Subtract by adding 9s complement of subtrahend to minuend First 9s complement algorithm Complement bits Add 1010 (decimal 10) and discard carry Second 9s complement algorithm Add 0110 (decimal 6) Complement bits

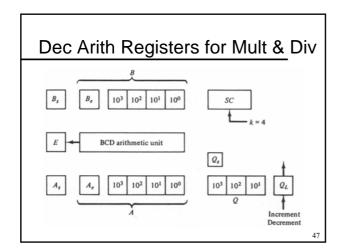

| Symbolic Designation     | Description                                         |

|--------------------------|-----------------------------------------------------|

| $A \leftarrow A + B$     | Add decimal numbers and transfer sum into $A$       |

| B                        | 9's complement of $B$                               |

| $A \leftarrow A + B + 1$ | Content of $A$ plus 10's complement of $B$ into $A$ |

| $Q_L \leftarrow Q_L + 1$ | Increment BCD number in $Q_L$                       |

| dshr A                   | Decimal shift-right register $A$                    |

| dshl A                   | Decimal shift-left register $A$                     |

| Decimal Division Flowchart                                                                                                     |    |

|--------------------------------------------------------------------------------------------------------------------------------|----|

| Divide<br>(There as 8<br>Division is 4.0<br>(Creak to contribute)                                                              |    |

|                                                                                                                                |    |

| $\begin{array}{c} \bullet \\ \bullet $ |    |

| 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                        | 49 |