## **Algorithms to Generate Distinguishing, Homing** and Synchronizing Sequences

#### Example : Consider FSM

| State table |             |             |  |  |

|-------------|-------------|-------------|--|--|

| present     | input       |             |  |  |

| state       | x=0         | x=1         |  |  |

| A           | B,0         | ,           |  |  |

| В           | A,0         | <b>B,</b> 0 |  |  |

| С           | <b>D</b> ,1 | A,0         |  |  |

| D           | <b>D</b> ,1 | С,0         |  |  |

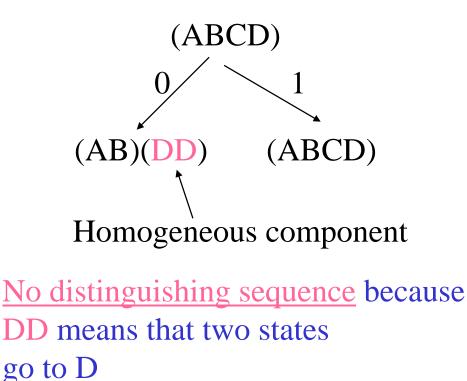

Algorithm to Generate a Distinguishing Sequence

**Distinguishing sequence** - path from root to a trivial vector.

A distinguishing tree is a successor tree in which a node becomes terminal if

- 1. Non-homogenous components in an uncertainty vector are the same as on the previous level

- 2. Uncertainty vector contains a homogeneous non-trivial component (does not have to be a homogeneous vector)

- 3. Uncertainty vector is trivial

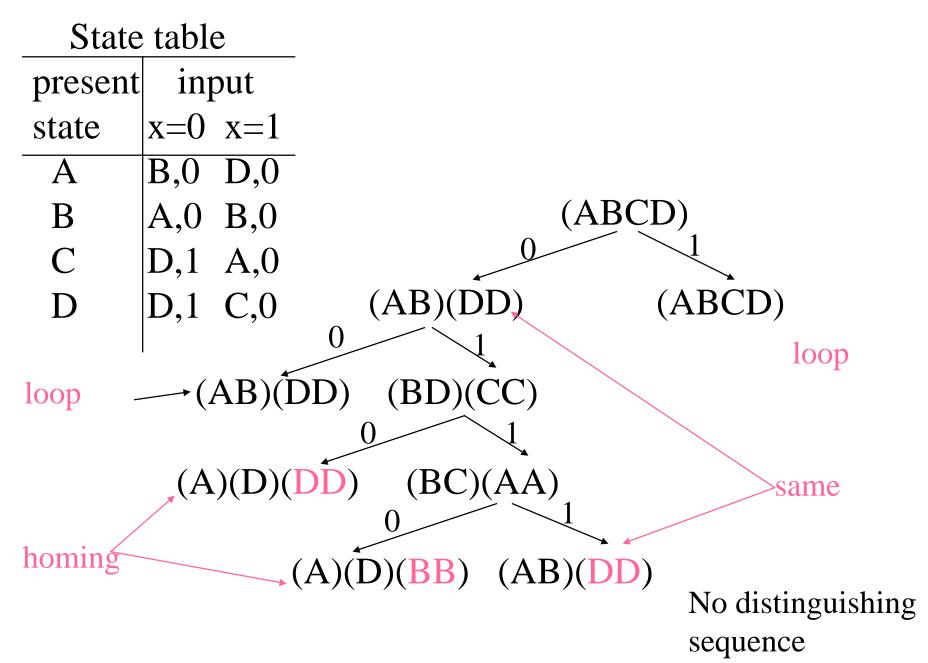

#### Example : continuation of the <u>same FSM</u>

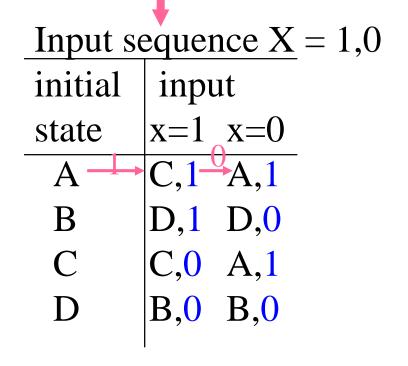

Example : Consider FSM, different output vectors for different initial state

| State table |       |             |  |  |

|-------------|-------|-------------|--|--|

| present     | input |             |  |  |

| state       | x=0   | x=1         |  |  |

| A           | A,0   | <b>C</b> ,1 |  |  |

| В           | B,0   | D,1         |  |  |

| С           | A,1   | <b>C,</b> 0 |  |  |

| D           | D,0   | <b>B,</b> 0 |  |  |

|             |       |             |  |  |

Each input state responds to 10 with different output sequence

so X=1,0 distinguishing

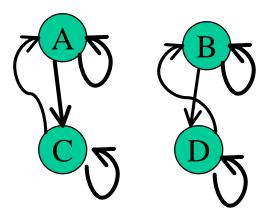

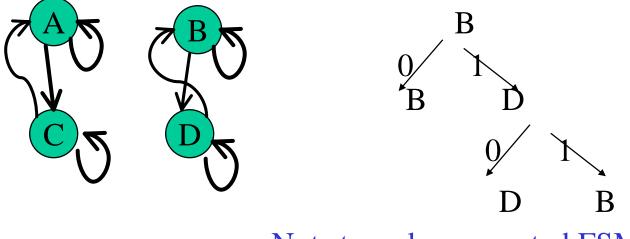

Transfer sequence - takes machine from one state to another Example : Consider previous FSM

We cannot reach A or C

Not strongly connected FSM

Example : Consider the following FSM

| State table |             |             |  |  |

|-------------|-------------|-------------|--|--|

| present     | input       |             |  |  |

| state       | x=0         | x=1         |  |  |

| А           | <b>B</b> ,1 | C,0         |  |  |

| В           | A,0         | D,1         |  |  |

| С           | B,0         | A,0         |  |  |

| D           | <b>C</b> ,1 | <b>A,</b> 1 |  |  |

|             |             |             |  |  |

Example : we get the transfer tree

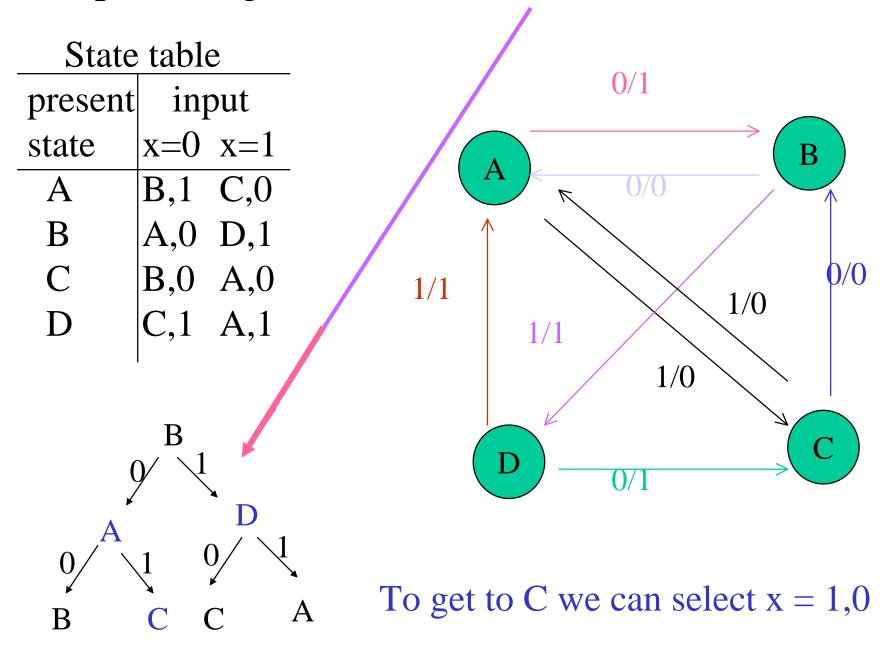

Synchronizing sequence takes machine to the specific final state regardless of the output or initial state - does not always exists

#### Example :

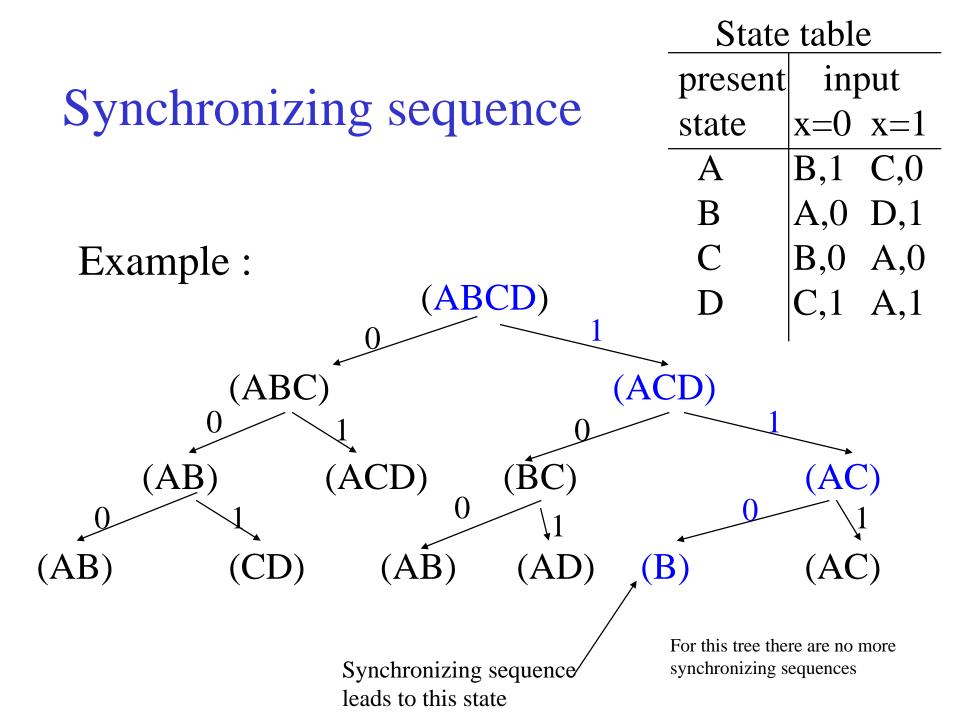

Algorithm to generate synchronizing sequence : Consider the previous machine with synchronizing sequence X = 1,1,0

Machine must be strongly connected & diagnosable (i.e. *have a distinguishing sequence*)

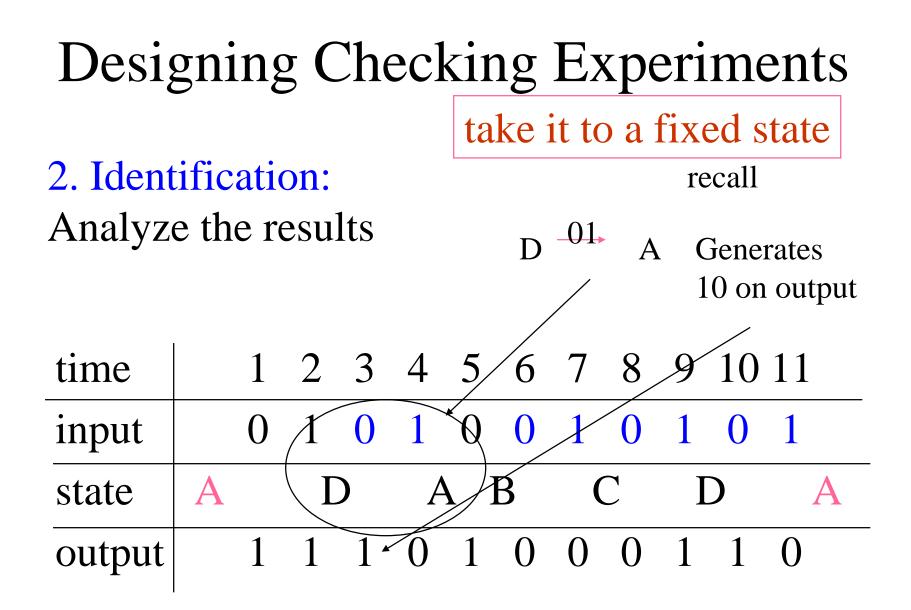

- **1**. Initialization (take it to a fixed state[s])

- a) Apply homing sequence & identify the current state

- b) Transfer current state to S

- 2. Identification (make machine to visit each state and display response)

- **3.** Transition verification (make every state transition result checked by distinguishing sequence)

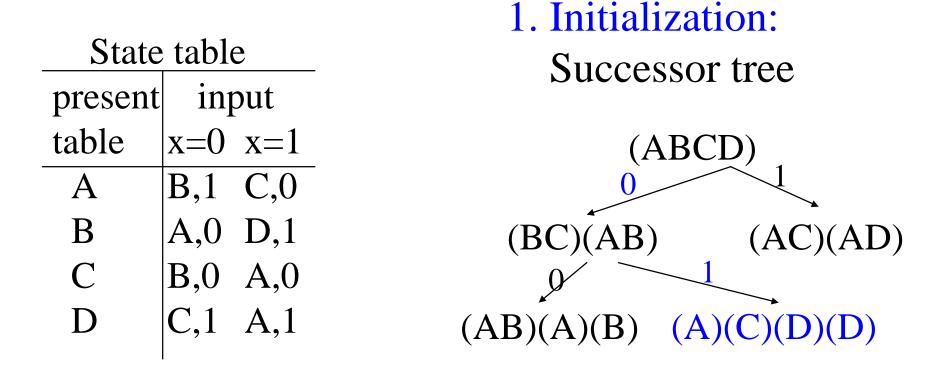

Example : Consider FSM

Homing sequence x = 0,1

Example (cont.) :

#### Response Table

| State table |             |     |  |  |

|-------------|-------------|-----|--|--|

| present     | inp         | out |  |  |

| table       | x=0         | x=1 |  |  |

| A           | <b>B</b> ,1 | •   |  |  |

| В           | A,0         | D,1 |  |  |

| С           | B,0         | A,0 |  |  |

| D           | <b>C</b> ,1 | A,1 |  |  |

| Initial          | Response       | final  |

|------------------|----------------|--------|

| states           | to 0 1         | states |

| A <sup>0</sup> → | B,1 <u>D,1</u> | D      |

| В                | A,0 C,0        | C      |

| С                | B,0 D,1        | D      |

| D                | C,1 A,0        | A      |

3. Transition verification:

Check transition from A to B with input 0, then apply distinguishing sequence 01

| time  |   | 1 | 2 | 3 |

|-------|---|---|---|---|

| input |   | 0 | 0 | 1 |

|       |   |   |   |   |

| state | A | ] | B | С |

**Example** : Check transition from C to B with input 0 and from C to A with input 1, and so on. The entire checking test

| time   | 1 2 3 4 5 6 7 8 9 10 11                                                                |  |

|--------|----------------------------------------------------------------------------------------|--|

| input  | 0 0 1 0 0 1 1 0 1 0 0                                                                  |  |

| state  | $A \rightarrow B \qquad C \rightarrow B \qquad C \rightarrow A \qquad D \rightarrow C$ |  |

| output | 1 0 0 0 0 0 0 1 1 1 0                                                                  |  |

# Designing Checking Experiments (cont)

| time   | 12 | 2 13 | 14 | 15 | 16 | 17 | 18 | 19  | 20 | 21 |

|--------|----|------|----|----|----|----|----|-----|----|----|

| input  | 1  | 1    | 0  | 1  | 0  | 1  | 0  | 0   | 0  | 1  |

| state  |    | D→.  | A  |    | D  |    | -  | B → | A  |    |

| output | 1  | 1    | 1  | 1  | 1  | 0  | 1  | 0   | 1  | 1  |

|        |    |      |    |    |    |    |    |     |    |    |

| time   | 22 | 2 23 | 24 | 25 | 26 | 27 | 28 | 29  | 30 | 31 |

| input  | 1  | 1    | 0  | 1  | 0  | 1  | 0  | 1   | 0  | 1  |

| state  | D  | A→   | С  | -  | D  |    | ]  | B→  | D  | A  |

| output | 1  | 0    | 0  | 1  | 1  | 0  | 1  | 1   | 1  | 0  |

#### Critical testability problems

- 1. Noninitializable design change design to have a synchronizing sequence

- 2. Effects of component delays check for hazard & races in simulation

- 3. Nondetected logic redundant faults do not use logic redundancy

- Existence of illegal states avoid; add transition to normal states

- 5. Oscillating circuit add extra logic to control oscillations

Checking experiments can not be applied for FSM <u>without a distinguishing sequence</u>

#### **Modification procedure** for such FSM:

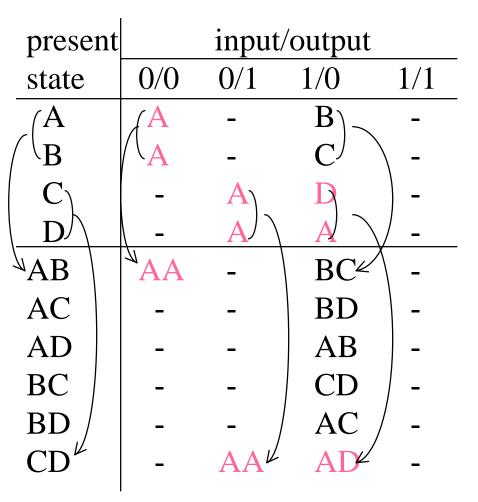

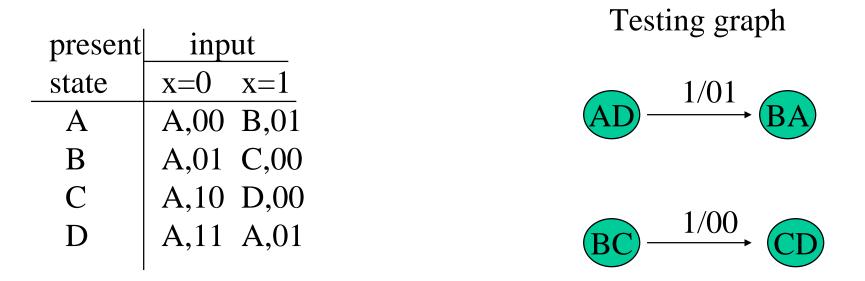

I. Construct testing table upper part contains states & input/output pairs, lower part contains products of present & next states with the rule that (state)\*(-) = (-)

II. Construct testing graph

#### **Example:**

state table

| present | input |             |  |

|---------|-------|-------------|--|

| state   | x=0   | x=1         |  |

| А       | A,0   | <b>B,</b> 0 |  |

| В       | A,0   | C,0         |  |

| С       | A,1   | D,0         |  |

| D       | A,1   | A,0         |  |

|         |       |             |  |

#### Testing table for machine

## Example (continued)

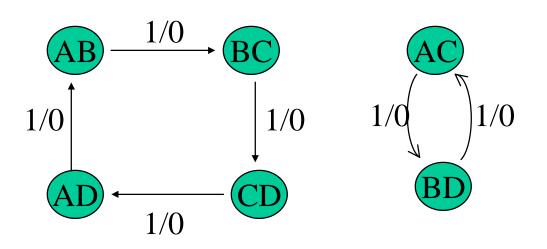

II. Construct testing graph

| present | input |     |

|---------|-------|-----|

| state   | x=0   | x=1 |

| А       | A,0   | В,0 |

| В       | A,0   | C,0 |

| С       | A,1   | D,0 |

| D       | A,1   | А,0 |

|         |       |     |

An edge  $X_p/Z_p$  exists directed from present state  $S_iS_j$  to next states  $S_kS_1$  if  $S_kS_1$  (k  $\neq 1$ ) is present in row  $S_iS_j$  under  $X_p/Z_p$

Example: for our machine we have:

### Example (continued)

| present | input       |             |  |

|---------|-------------|-------------|--|

| state   | x=0         | x=1         |  |

| А       | A,0         | B,0         |  |

| В       | A,0         | <b>C,</b> 0 |  |

| С       | <b>A,</b> 1 | D,0         |  |

| D       | A,1         | A,0         |  |

|         |             |             |  |

Now we can modify the graph by adding output(s)

First introduce new concept of definitely diagnosable

Example: for our machine we have:

## **DFT for Sequential Circuits (cont)**

A machine is <u>definitely diagnosable</u> if its testing graph has <u>no loops</u> and there are <u>no repeated states</u> (i.e. no circled states in testing table)

In order to make machine *definitely diagnosable* <u>additional outputs</u> (up to k = log (# states)) <u>are</u> *required*

Coming back to our Example: (with added output)

Now the machine has a distinguishing sequence

After machine is *modified to have distinguishing sequence* apply checking experiment procedure to test it.

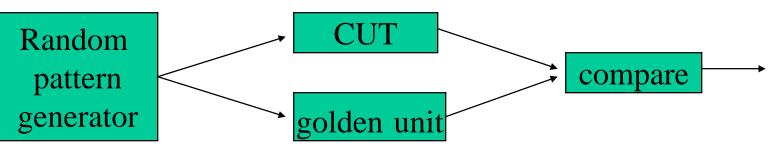

## **Random Testing**

Reduce computation time

- 1. Random sequence is stored as a test when it can detect fault, then this fault is detected from the fault list and another random sequence is checked

- 2. Output of CUT (circuit under test ) is compared with this "golden unit"

Two approaches Is it good for FSMs?

#### **Two approaches :**

#### Sources

• Starzyk, Ohio University