2. IMPLEMENTATION

2.1 Description

2.2 System Block

Diagram

2.3 VHDL Source Code Listing

and Description

comp.vhd

evensort.vhd

newsort.vhd

oddsort.vhd

sortdone.vhd

sorter.vhd -- top level

3. SIMULATION

sorter.do

sorter.ps

Look at different sorting variations -- pipelined, combinatorial, two-register, one-register, Kashubin's sorter/absorber project, etc. and design a sorting circuit (of any kind) that utilizes any of the ideas listed above. The circuit has to be implemented in VHDL, but any style -- behavioral, functional, or structural -- is acceptable. The circuit does not have to be synthesizable. Provide simulation results to prove the correctness of the design.

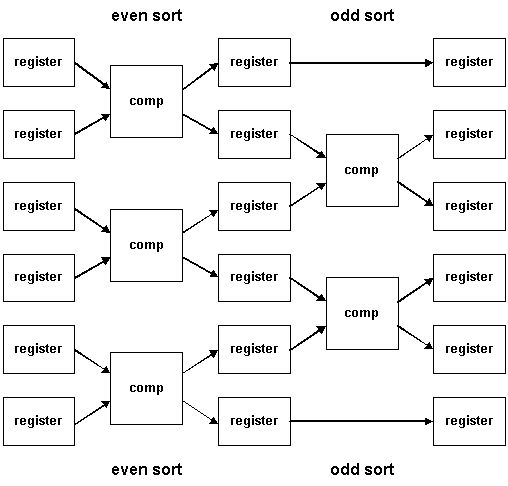

This sorter is designed to sort eight 3-bit numbers in either direction -- ascending or descending. The sorting algorithm is adapted from Kashubin's Sorter/Absorber project. The data to be sorted is stored in the registers and sorted using even or odd sorting. The algorithm is illustrated in Figure 1.

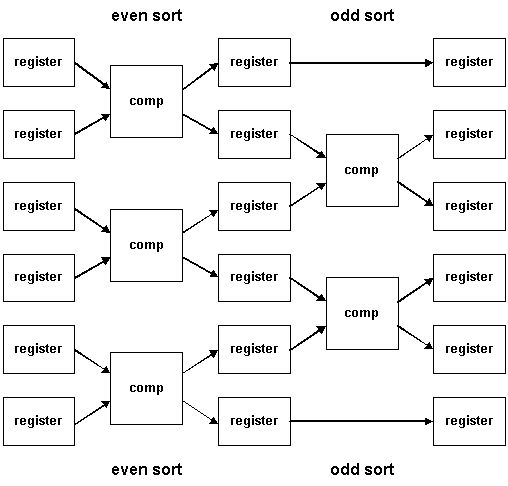

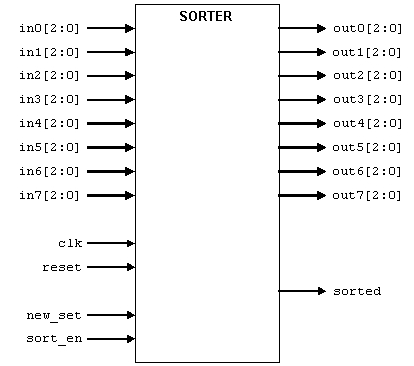

The top level of the sorter consists of eight 3-bit inputs (in[0:7]) and eight 3-bit outputs (out[0:7]) with control signals, dir_of_sort, new_set, reset, sort_en, and an output signal, sorted. The flip-flops are clocked with clk, which can be running at any speed. (This is true for functional simulations only. For an actual FPGA implementation, the maximum clock speed depends on the speed grade of the particular device.) The top-level block diagram is illustrated in Figure 2, and the signals are listed and described in Table 1.

Table 1 Description of Top-Level Signals

Signal Length Type (bit) Description in[0:7] 3 in Input data to be sorted. out[0:7] 3 out Output data that is sorted when sorted is asserted. clk 1 in System clock. dir_of_sort 1 in Direction of sort. If '1' => ascending (out0 = min, out7 = max); if '0' => descending (out0 = max, out7 = min.) new_set 1 in If asserted, in[0:7] contains a new set of data to be sorted. reset 1 in System reset. Reset all flip-flops if asserted. sort_en 1 in sorted output enable. sorted 1 out out[0:7] contains the sorted data if asserted.

back to top

The output of ODDSORT is connected to SORTDONE, which is a logic block that verifies the sorted results. sorted is asserted if the data is sorted in the direction desired and sort_en is asserted. sorted stays asserted as long as sort_en is asserted.

The function of NEWSORT is to check new_set and determine if the output of ODDSORT or the data from the external in port should be routed to the input of EVENSORT. If new_set is asserted, the data at the in port should be selected to initiate a new sort.

This modulde is designed to compare two 3-bit numbers, num0_in and num1_in, and determine whether to switch the numbers according to the direction of the comparison. If dir_of_sort = '1' (ascending), then the output num0_out should be less than or equal to output num1_out; if dir_of_sort = '0' (descending), then output num0_out should be greater than or equal to output num1_out.

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_arith.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY comp IS

PORT (

clk

: IN std_logic;

dir_of_sort : IN bit;

reset

: IN bit;

num0_in

: IN bit_vector (2 DOWNTO 0);

num1_in

: IN bit_vector (2 DOWNTO 0);

num0_out

: OUT bit_vector (2 DOWNTO 0);

num1_out

: OUT bit_vector (2 DOWNTO 0)

);

END ENTITY comp;

ARCHITECTURE compare OF comp IS

BEGIN

PROCESS (reset, clk)

BEGIN

-- reset everything to

'0' when reset is asserted

IF (reset = '1') THEN

num0_out <= (OTHERS => '0');

num1_out <= (OTHERS => '0');

-- the flip-flops are

sensitive to the rising edge of clk

ELSIF (rising_edge (clk))

THEN

CASE dir_of_sort IS

-- direction of sort is ascending

WHEN '1' =>

-- num0_in is greater than num1_in, so switch them

IF (num0_in > num1_in) THEN

num0_out <= num1_in;

num1_out <= num0_in;

-- num0_in and num1_in are in order

ELSE

num0_out <= num0_in;

num1_out <= num1_in;

END IF;

-- direction of sort is descending

WHEN '0' =>

-- num0_in is less than num1_in, so switch them

IF (num0_in < num1_in) THEN

num0_out <= num1_in;

num1_out <= num0_in;

-- num0_in and num1_in are in order

ELSE

num0_out <= num0_in;

num1_out <= num1_in;

END IF;

END CASE;

END IF;

END PROCESS;

END ARCHITECTURE compare;

EVENSORT takes the eight 3-bit numbers, sort them in desired direction using the even sorting algorithm, and output the resulting numbers. The module utilizes the COMP.VHD module to perform the actual data comparison.

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_arith.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY even_sort IS

PORT (

clk

: IN std_logic;

dir_of_sort : IN bit;

reset

: IN bit;

even_in0

: IN bit_vector (2 DOWNTO 0);

even_in1

: IN bit_vector (2 DOWNTO 0);

even_in2

: IN bit_vector (2 DOWNTO 0);

even_in3

: IN bit_vector (2 DOWNTO 0);

even_in4

: IN bit_vector (2 DOWNTO 0);

even_in5

: IN bit_vector (2 DOWNTO 0);

even_in6

: IN bit_vector (2 DOWNTO 0);

even_in7

: IN bit_vector (2 DOWNTO 0);

even_out0

: OUT bit_vector (2 DOWNTO 0);

even_out1

: OUT bit_vector (2 DOWNTO 0);

even_out2

: OUT bit_vector (2 DOWNTO 0);

even_out3

: OUT bit_vector (2 DOWNTO 0);

even_out4

: OUT bit_vector (2 DOWNTO 0);

even_out5

: OUT bit_vector (2 DOWNTO 0);

even_out6

: OUT bit_vector (2 DOWNTO 0);

even_out7

: OUT bit_vector (2 DOWNTO 0)

);

END ENTITY even_sort;

ARCHITECTURE even_sorter OF even_sort IS

-- use this module to perform data comparison

COMPONENT comp IS

PORT (

clk : IN std_logic;

dir_of_sort : IN bit;

reset : IN bit;

num0_in : IN bit_vector

(2 DOWNTO 0);

num1_in : IN bit_vector

(2 DOWNTO 0);

num0_out : OUT bit_vector

(2 DOWNTO 0);

num1_out : OUT bit_vector

(2 DOWNTO 0)

);

END COMPONENT comp;

BEGIN

-- sort data0 and data1

even_comp1:comp

PORT MAP (clk, dir_of_sort, reset, even_in0, even_in1, even_out0,

even_out1);

-- sort data2 and data3

even_comp2:comp

PORT MAP (clk, dir_of_sort, reset, even_in2, even_in3, even_out2,

even_out3);

-- sort data4 and data5

even_comp3:comp

PORT MAP (clk, dir_of_sort, reset, even_in4, even_in5, even_out4,

even_out5);

-- sort data6 and data7

even_comp4:comp

PORT MAP (clk, dir_of_sort, reset, even_in6, even_in7, even_out6,

even_out7);

END ARCHITECTURE even_sorter;

This is simply a multiplexer that lets either one of the two different sets of data through depending on the value of new_set. If new_set is asserted, the set of data from the 'in' port is selected and sent to the even sorting module; otherwise, the set of data from the output of the odd sorting module is selected, permitting the sorting to continue.

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_arith.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY new_sort IS

PORT (

new_set : IN bit;

reset

: IN bit;

old_in0 : IN bit_vector

(2 DOWNTO 0);

old_in1 : IN bit_vector

(2 DOWNTO 0);

old_in2 : IN bit_vector

(2 DOWNTO 0);

old_in3 : IN bit_vector

(2 DOWNTO 0);

old_in4 : IN bit_vector

(2 DOWNTO 0);

old_in5 : IN bit_vector

(2 DOWNTO 0);

old_in6 : IN bit_vector

(2 DOWNTO 0);

old_in7 : IN bit_vector

(2 DOWNTO 0);

new_in0 : IN bit_vector

(2 DOWNTO 0);

new_in1 : IN bit_vector

(2 DOWNTO 0);

new_in2 : IN bit_vector

(2 DOWNTO 0);

new_in3 : IN bit_vector

(2 DOWNTO 0);

new_in4 : IN bit_vector

(2 DOWNTO 0);

new_in5 : IN bit_vector

(2 DOWNTO 0);

new_in6 : IN bit_vector

(2 DOWNTO 0);

new_in7 : IN bit_vector

(2 DOWNTO 0);

mux_out0 : OUT bit_vector

(2 DOWNTO 0);

mux_out1 : OUT bit_vector

(2 DOWNTO 0);

mux_out2 : OUT bit_vector

(2 DOWNTO 0);

mux_out3 : OUT bit_vector

(2 DOWNTO 0);

mux_out4 : OUT bit_vector

(2 DOWNTO 0);

mux_out5 : OUT bit_vector

(2 DOWNTO 0);

mux_out6 : OUT bit_vector

(2 DOWNTO 0);

mux_out7 : OUT bit_vector

(2 DOWNTO 0)

);

END ENTITY new_sort;

ARCHITECTURE mux OF new_sort IS

BEGIN

PROCESS (reset, new_set, new_in0, new_in1, new_in2,

new_in3, new_in4,

new_in5, new_in6, new_in7, old_in0, old_in1, old_in2,

old_in3, old_in4, old_in5, old_in6, old_in7)

BEGIN

-- reset everything

to '0' when reset is asserted

IF (reset = '1') THEN

mux_out0 <= (OTHERS => '0');

mux_out1 <= (OTHERS => '0');

mux_out2 <= (OTHERS => '0');

mux_out3 <= (OTHERS => '0');

mux_out4 <= (OTHERS => '0');

mux_out5 <= (OTHERS => '0');

mux_out6 <= (OTHERS => '0');

mux_out7 <= (OTHERS => '0');

ELSE

-- if new_set is asserted, the mux output should contain the

-- new set of data

IF (new_set = '1') THEN

mux_out0 <= new_in0;

mux_out1 <= new_in1;

mux_out2 <= new_in2;

mux_out3 <= new_in3;

mux_out4 <= new_in4;

mux_out5 <= new_in5;

mux_out6 <= new_in6;

mux_out7 <= new_in7;

-- otherwise, let the old data coming out of odd sort through

ELSE

mux_out0 <= old_in0;

mux_out1 <= old_in1;

mux_out2 <= old_in2;

mux_out3 <= old_in3;

mux_out4 <= old_in4;

mux_out5 <= old_in5;

mux_out6 <= old_in6;

mux_out7 <= old_in7;

END IF;

END IF;

END PROCESS;

END ARCHITECTURE mux;

ODDSORT takes the eight 3-bit numbers, sort them in desired direction using the odd sorting algorithm, and output the resulting numbers. The module utilizes the COMP.VHD module to perform the actual data comparison.

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_arith.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY odd_sort IS

PORT (

clk

: IN std_logic;

dir_of_sort : IN bit;

reset

: IN bit;

odd_in0

: IN bit_vector (2 DOWNTO 0);

odd_in1

: IN bit_vector (2 DOWNTO 0);

odd_in2

: IN bit_vector (2 DOWNTO 0);

odd_in3

: IN bit_vector (2 DOWNTO 0);

odd_in4

: IN bit_vector (2 DOWNTO 0);

odd_in5

: IN bit_vector (2 DOWNTO 0);

odd_in6

: IN bit_vector (2 DOWNTO 0);

odd_in7

: IN bit_vector (2 DOWNTO 0);

odd_out0

: OUT bit_vector (2 DOWNTO 0);

odd_out1

: OUT bit_vector (2 DOWNTO 0);

odd_out2

: OUT bit_vector (2 DOWNTO 0);

odd_out3

: OUT bit_vector (2 DOWNTO 0);

odd_out4

: OUT bit_vector (2 DOWNTO 0);

odd_out5

: OUT bit_vector (2 DOWNTO 0);

odd_out6

: OUT bit_vector (2 DOWNTO 0);

odd_out7

: OUT bit_vector (2 DOWNTO 0)

);

END ENTITY odd_sort;

ARCHITECTURE odd_sorter OF odd_sort IS

-- use this module to perform data comparison

COMPONENT comp IS

PORT (

clk

: IN std_logic;

dir_of_sort : IN bit;

reset

: IN bit;

num0_in

: IN bit_vector (2 DOWNTO 0);

num1_in

: IN bit_vector (2 DOWNTO 0);

num0_out

: OUT bit_vector (2 DOWNTO 0);

num1_out

: OUT bit_vector (2 DOWNTO 0)

);

END COMPONENT comp;

BEGIN

PROCESS (reset, clk)

BEGIN

-- reset everything

to '0' if reset is asserted

IF (reset = '1') THEN

odd_out0 <= (OTHERS => '0');

odd_out7 <= (OTHERS => '0');

-- send data0 and data7

straight through

ELSIF (rising_edge (clk))

THEN

odd_out0 <= odd_in0;

odd_out7 <= odd_in7;

END IF;

END PROCESS;

-- sort data1 and data2

odd_comp1:comp

PORT MAP (clk, dir_of_sort, reset, odd_in1, odd_in2, odd_out1,

odd_out2);

-- sort data3 and data4

odd_comp2:comp

PORT MAP (clk, dir_of_sort, reset, odd_in3, odd_in4, odd_out3,

odd_out4);

-- sort data5 and data6

odd_comp3:comp

PORT MAP (clk, dir_of_sort, reset, odd_in5, odd_in6, odd_out5,

odd_out6);

END ARCHITECTURE odd_sorter;

This module determines if the input data is sorted in desired order (ascending from in0 if dir_of_sort = '1', descending if dir_of_sort = '0'.) If the data is sorted and sort_en is asserted, sorted is asserted until sort_en is cleared.

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_arith.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY sort_done IS

PORT (

dir_of_sort : IN bit;

reset

: IN bit;

sort_en

: IN bit;

num0

: IN bit_vector (2 DOWNTO 0);

num1

: IN bit_vector (2 DOWNTO 0);

num2

: IN bit_vector (2 DOWNTO 0);

num3

: IN bit_vector (2 DOWNTO 0);

num4

: IN bit_vector (2 DOWNTO 0);

num5

: IN bit_vector (2 DOWNTO 0);

num6

: IN bit_vector (2 DOWNTO 0);

num7

: IN bit_vector (2 DOWNTO 0);

sorted

: OUT bit

);

END ENTITY sort_done;

ARCHITECTURE verify OF sort_done IS

BEGIN

PROCESS (reset, dir_of_sort, sort_en, num0,

num1, num2, num3, num4,

num5, num6, num7)

BEGIN

IF (reset = '1') THEN

sorted <= '0';

ELSE

CASE dir_of_sort IS

-- direction of sort is ascending (num0 = min, num7 = max),

-- so check to see if all inputs are in desired order;

-- assert sorted if sort_en is asserted and all numbers are

-- in order

WHEN '1' =>

IF (sort_en = '1' AND num0 <= num1 AND num1 <= num2 AND

num2 <= num3 AND num3 <= num4 AND num4 <= num5 AND

num5 <= num6 AND num6 <= num7) THEN

sorted <= '1';

ELSE

sorted <= '0';

END IF;

-- direction of sort is descending (num0 = max, num7 = min),

-- so check to see if all inputs are in desired order;

-- assert sorted if sort_en is asserted and all numbers are

-- in order

WHEN '0' =>

IF (sort_en = '1' AND num0 >= num1 AND num1 >= num2 AND

num2 >= num3 AND num3 >= num4 AND num4 >= num5 AND

num5 >= num6 AND num6 >= num7) THEN

sorted <= '1';

ELSE

sorted <= '0';

END IF;

END CASE;

END IF;

END PROCESS;

END ARCHITECTURE verify;

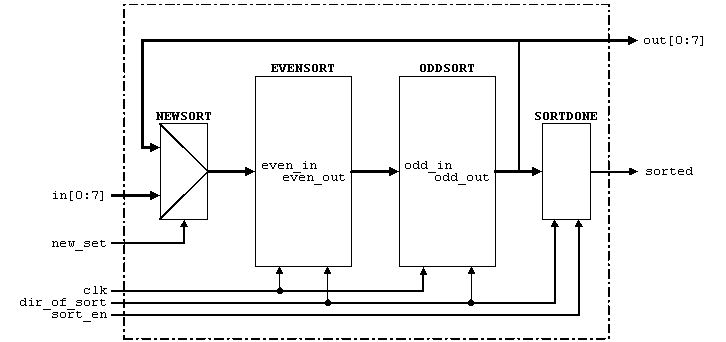

This is the top level of the sorter design. All the signals are connected through this module except for signals from COMP.VHD, which is called by EVENSORT and ODDSORT only.

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_arith.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY sorter IS

PORT (

clk

: IN std_logic;

dir_of_sort : IN bit;

new_set

: IN bit;

reset

: IN bit;

sort_en

: IN bit;

in0

: IN bit_vector (2 DOWNTO 0);

in1

: IN bit_vector (2 DOWNTO 0);

in2

: IN bit_vector (2 DOWNTO 0);

in3

: IN bit_vector (2 DOWNTO 0);

in4

: IN bit_vector (2 DOWNTO 0);

in5

: IN bit_vector (2 DOWNTO 0);

in6

: IN bit_vector (2 DOWNTO 0);

in7

: IN bit_vector (2 DOWNTO 0);

out0

: INOUT bit_vector (2 DOWNTO 0);

out1

: INOUT bit_vector (2 DOWNTO 0);

out2

: INOUT bit_vector (2 DOWNTO 0);

out3

: INOUT bit_vector (2 DOWNTO 0);

out4

: INOUT bit_vector (2 DOWNTO 0);

out5

: INOUT bit_vector (2 DOWNTO 0);

out6

: INOUT bit_vector (2 DOWNTO 0);

out7

: INOUT bit_vector (2 DOWNTO 0);

sorted

: OUT bit

);

END ENTITY sorter;

ARCHITECTURE sort OF sorter IS

SIGNAL mux_even0 : bit_vector (2 DOWNTO 0);

SIGNAL mux_even1 : bit_vector (2 DOWNTO 0);

SIGNAL mux_even2 : bit_vector (2 DOWNTO 0);

SIGNAL mux_even3 : bit_vector (2 DOWNTO 0);

SIGNAL mux_even4 : bit_vector (2 DOWNTO 0);

SIGNAL mux_even5 : bit_vector (2 DOWNTO 0);

SIGNAL mux_even6 : bit_vector (2 DOWNTO 0);

SIGNAL mux_even7 : bit_vector (2 DOWNTO 0);

SIGNAL even_odd0 : bit_vector (2 DOWNTO 0);

SIGNAL even_odd1 : bit_vector (2 DOWNTO 0);

SIGNAL even_odd2 : bit_vector (2 DOWNTO 0);

SIGNAL even_odd3 : bit_vector (2 DOWNTO 0);

SIGNAL even_odd4 : bit_vector (2 DOWNTO 0);

SIGNAL even_odd5 : bit_vector (2 DOWNTO 0);

SIGNAL even_odd6 : bit_vector (2 DOWNTO 0);

SIGNAL even_odd7 : bit_vector (2 DOWNTO 0);

COMPONENT even_sort IS

PORT (

clk

: IN std_logic;

dir_of_sort : IN bit;

reset

: IN bit;

even_in0

: IN bit_vector (2 DOWNTO 0);

even_in1

: IN bit_vector (2 DOWNTO 0);

even_in2

: IN bit_vector (2 DOWNTO 0);

even_in3

: IN bit_vector (2 DOWNTO 0);

even_in4

: IN bit_vector (2 DOWNTO 0);

even_in5

: IN bit_vector (2 DOWNTO 0);

even_in6

: IN bit_vector (2 DOWNTO 0);

even_in7

: IN bit_vector (2 DOWNTO 0);

even_out0

: OUT bit_vector (2 DOWNTO 0);

even_out1

: OUT bit_vector (2 DOWNTO 0);

even_out2

: OUT bit_vector (2 DOWNTO 0);

even_out3

: OUT bit_vector (2 DOWNTO 0);

even_out4

: OUT bit_vector (2 DOWNTO 0);

even_out5

: OUT bit_vector (2 DOWNTO 0);

even_out6

: OUT bit_vector (2 DOWNTO 0);

even_out7

: OUT bit_vector (2 DOWNTO 0)

);

END COMPONENT even_sort;

COMPONENT new_sort IS

PORT (

new_set : IN bit;

reset

: IN bit;

old_in0 : IN bit_vector

(2 DOWNTO 0);

old_in1 : IN bit_vector

(2 DOWNTO 0);

old_in2 : IN bit_vector

(2 DOWNTO 0);

old_in3 : IN bit_vector

(2 DOWNTO 0);

old_in4 : IN bit_vector

(2 DOWNTO 0);

old_in5 : IN bit_vector

(2 DOWNTO 0);

old_in6 : IN bit_vector

(2 DOWNTO 0);

old_in7 : IN bit_vector

(2 DOWNTO 0);

new_in0 : IN bit_vector

(2 DOWNTO 0);

new_in1 : IN bit_vector

(2 DOWNTO 0);

new_in2 : IN bit_vector

(2 DOWNTO 0);

new_in3 : IN bit_vector

(2 DOWNTO 0);

new_in4 : IN bit_vector

(2 DOWNTO 0);

new_in5 : IN bit_vector

(2 DOWNTO 0);

new_in6 : IN bit_vector

(2 DOWNTO 0);

new_in7 : IN bit_vector

(2 DOWNTO 0);

mux_out0 : OUT bit_vector

(2 DOWNTO 0);

mux_out1 : OUT bit_vector

(2 DOWNTO 0);

mux_out2 : OUT bit_vector

(2 DOWNTO 0);

mux_out3 : OUT bit_vector

(2 DOWNTO 0);

mux_out4 : OUT bit_vector

(2 DOWNTO 0);

mux_out5 : OUT bit_vector

(2 DOWNTO 0);

mux_out6 : OUT bit_vector

(2 DOWNTO 0);

mux_out7 : OUT bit_vector

(2 DOWNTO 0)

);

END COMPONENT new_sort;

COMPONENT odd_sort IS

PORT (

clk

: IN std_logic;

dir_of_sort : IN bit;

reset

: IN bit;

odd_in0

: IN bit_vector (2 DOWNTO 0);

odd_in1

: IN bit_vector (2 DOWNTO 0);

odd_in2

: IN bit_vector (2 DOWNTO 0);

odd_in3

: IN bit_vector (2 DOWNTO 0);

odd_in4

: IN bit_vector (2 DOWNTO 0);

odd_in5

: IN bit_vector (2 DOWNTO 0);

odd_in6

: IN bit_vector (2 DOWNTO 0);

odd_in7

: IN bit_vector (2 DOWNTO 0);

odd_out0

: OUT bit_vector (2 DOWNTO 0);

odd_out1

: OUT bit_vector (2 DOWNTO 0);

odd_out2

: OUT bit_vector (2 DOWNTO 0);

odd_out3

: OUT bit_vector (2 DOWNTO 0);

odd_out4

: OUT bit_vector (2 DOWNTO 0);

odd_out5

: OUT bit_vector (2 DOWNTO 0);

odd_out6

: OUT bit_vector (2 DOWNTO 0);

odd_out7

: OUT bit_vector (2 DOWNTO 0)

);

END COMPONENT odd_sort;

COMPONENT sort_done IS

PORT (

dir_of_sort : IN bit;

reset

: IN bit;

sort_en

: IN bit;

num0

: IN bit_vector (2 DOWNTO 0);

num1

: IN bit_vector (2 DOWNTO 0);

num2

: IN bit_vector (2 DOWNTO 0);

num3

: IN bit_vector (2 DOWNTO 0);

num4

: IN bit_vector (2 DOWNTO 0);

num5

: IN bit_vector (2 DOWNTO 0);

num6

: IN bit_vector (2 DOWNTO 0);

num7

: IN bit_vector (2 DOWNTO 0);

sorted

: OUT bit

);

END COMPONENT sort_done;

BEGIN

es:even_sort

PORT MAP (clk, dir_of_sort, reset, mux_even0, mux_even1, mux_even2,

mux_even3,

mux_even4, mux_even5, mux_even6, mux_even7,

even_odd0,

even_odd1, even_odd2, even_odd3, even_odd4,

even_odd5,

even_odd6, even_odd7);

ns:new_sort

PORT MAP (new_set, reset, out0, out1, out2, out3, out4, out5, out6,

out7, in0,

in1, in2, in3, in4, in5, in6, in7, mux_even0,

mux_even1,

mux_even2, mux_even3, mux_even4, mux_even5,

mux_even6,

mux_even7);

os:odd_sort

PORT MAP (clk, dir_of_sort, reset, even_odd0, even_odd1, even_odd2,

even_odd3,

even_odd4, even_odd5, even_odd6, even_odd7, out0,

out1, out2,

out3, out4, out5, out6, out7);

sd:sort_done

PORT MAP (dir_of_sort, reset, sort_en, out0, out1, out2, out3,

out4,

out5, out6,

out7, sorted);

END ARCHITECTURE sort;

The VHDL design is compiled and simulated using ModelSim by Model Technology. Three sets of binary numbers (presented in decimal below) are tested during the simulation (in0 - in7 ):

Set #1 -- 0, 1, 2, 3, 4,

5, 6, 7.

Set #2 -- 7, 6, 5, 4, 3,

2, 1, 0.

Set #3 -- 6, 3, 4, 3, 1,

5, 4, 7.

The sorter is instructed to sort these numbers in both directions. The final results are stored in out[0:7] until a new set of data is piped through the pipeline.

When a new set of data arrives, it takes two clock cycles for the new data to propagate through the pipeline, so new_set has to be asserted for at least two clock cycles; otherwise, the wrong set of data will be selected by the multiplexer NEWSORT. Same principle applies to sort_en: it can not be asserted until new_set is cleared because the sorted data will stay in the sorted order until the new data is piped through; otherwise, sorted will stay asserted when the new set of data is accepted. Toggling dir_of_sort solves the timing problem, but it is not always necessary to toggle the bit.

The simulation waveform is saved in sorter.ps. The clock rate

is 10 MHz. The following is the .do file developed for this simulation:

# begin sorter.do

force clk 0 50, 1 100 -repeat 100

force dir_of_sort 1

force new_set 0 0, 1 100, 0 300

force sort_en 0 0, 1 300

force in0 "000"

force in1 "001"

force in2 "010"

force in3 "011"

force in4 "100"

force in5 "101"

force in6 "110"

force in7 "111"

run 400

force dir_of_sort 0

force new_set 1 0, 0 200

force sort_en 0 0, 1 200

run 900

force new_set 1 0, 0 200

force sort_en 0 0, 1 200

force in7 "000"

force in6 "001"

force in5 "010"

force in4 "011"

force in3 "100"

force in2 "101"

force in1 "110"

force in0 "111"

run 300

force dir_of_sort 1

force new_set 1 0, 0 200

force sort_en 0 0, 1 200

run 900

force new_set 1 0, 0 200

force sort_en 0 0, 1 200

force in0 "110"

force in1 "011"

force in2 "100"

force in3 "011"

force in4 "001"

force in5 "101"

force in6 "100"

force in7 "111"

run 700

force dir_of_sort 0

force new_set 1 0, 0 200

force sort_en 0 0, 1 200

run 900

force sort_en 0

run 500

# end sorter.do