#### Data Flow Modeling in VHDL

# ECE-331, Digital Design Prof. Hintz Electrical and Computer Engineering

# Modeling Styles

- **Behavioral Modeling** Explicit definition of mathematical relationship between the input and output No implementation information Structural Modeling Implicit definition of I/O relationship through particular structure

- Interconnection of components

# **Behavioral Modeling**

All VHDL processes execute concurrently Non-procedural Data-flow Concurrent execution Procedural Algorithmic Sequential execution of statements Equivalent to a single concurrent statement

# Data Flow Model

Concurrent Statements

Execute in arbitrary order

Execute only when any of input variables changes

Local\_Sig\_1 <= In\_1 AND In\_2 ;

Local\_Sig\_2 <= In\_1 OR Local\_Sig\_1;

# Signal Assignment Statements

#### Two Types

- Conditional concurrent signal assignment statement

- Selected concurrent signal assignment statement

- Each of These Has a Sequential Process Equivalent

- Either Form Can Be Used and Are Equivalent

# Other Statements

#### Null Statements

#### Loop Statements

#### Assertion & Report Statements

6

# **Conditional Statements**

The Value of an Expression Is Assigned to a Signal When A Condition Is Evaluated As True

Condition Must Evaluate to a BOOLEAN

# **BIT or BOOLEAN?**

Logical Types Are Not Equal

BIT for signals

'0' or '1'

Character type

BOOLEAN for conditions

TRUE or FALSE

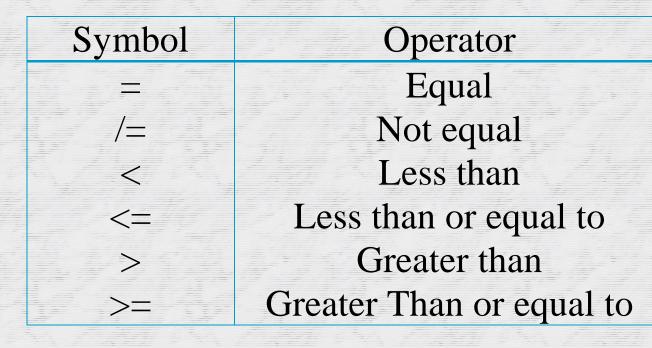

## **Relational Operators**

#### Relational Operators Have No Relative Precedence

# **Conditional Concurrent Syntax**

signal\_identifier <= options</pre>

conditional\_waveforms ;

options <=

[ guarded ] [ delay\_mechanisms ]

conditional\_waveforms <=

{ waveform when condition else }

waveform [ when condition ]</pre>

# Waveform Syntax

waveform <=

#### (value\_expression [ after time\_expression ] )

. . . . .

11

# Sequential Equivalent, If

[ if\_label : ] if Boolean\_expression

then

sequential\_statement

{ elsif Boolean\_expression then

sequential\_statement }

[ else

sequential\_statement ]

end if [ if\_label ] ;

# If Statement, e.g.,

entity NiCadCharger is

port ( Voltage, Current : in real ;

AC : in bit ;

Charged, Recharge : out bit);

end entity NiCadCharger ;

# If Statement, e.g.,

architecture ChargerArch1 of NiCadCharger

is

begin

Charger\_A: process (Voltage,

Current, AC ) is

begin

if Voltage >= 9.6 then

Charged <= `1';

Recharge <= `0';</pre>

# If Statement, e.g.,

elseif( AC = `1' and Current < 0.5 )

then</pre>

Charged <= `0';

Recharge <= `1';</pre>

#### else

Charged <= `0'; Recharge <= `0'; end process Charger\_A ; end architecture ChargerArch1 ;

# Select Conditional Statements

The Particular Value of an Expression Determines Which Statements Are Executed

The Sequential Equivalent To the Select Concurrent Conditional Assignment Statement Is The Case Statement

# Select Concurrent Syntax

with expression select

signal\_identifier <= options</pre>

selected\_waveforms ;

selected\_waveforms <=

{ waveform when choices , }

waveform when choices</pre>

# Case Statement Syntax

[ case\_label : ] case expression is

( when choices =>

{ sequential\_statement } )

{ ... }

end case [ case\_label ] ;

# Alternatives for "choices"

choices <= (

simple\_expression

discrete\_range

element\_simple\_name

others )</pre>

. . .

# Choices in Case Statements

Locally Static, Determined During Analysis Phase

Exactly One Choice for Each Possible Value of Selector Expression

More Than One Choice Can Be Listed for Each When

**Others**: Precedes the Alternative to Be Used If All Other Case Alternatives Fail

# Case Statement, e.g.,

# Case Statement, e.g.,

4\_to\_1\_MUX :

case MuxSelect is

when 0 =>

MuxOut <= In\_0 ;

when 1 =>

MuxOut <= In\_1 ;</pre>

# Case Statement, e.g.,

when 2 =>

MuxOut <= In\_2 ;

when 3 =>

MuxOut <= In\_3 ;

end case 4\_to\_1\_MUX ;</pre>

#### Null Statements

Need Method of Specifying When No Action Is to Be Performed, e.g., In Case Statement [ null\_label : ] null ; Use As "Stub" for Code to Be Written FlirFocus: process ( range, aperture ) begin null ;

end process FlirFocus ;

#### Loop Statements

Used for Repeated Execution of Sequential Statements Infinite

- Exit on condition

- Inner & Outer Loops

- Next

- While

- For

# Loop Statement Syntax

[ loop\_label : ]

loop { sequential\_statement }

end loop [ loop\_label ] ;

# Infinite Loop Example

entity 2\_Phase\_Clock is

port ( Clk : in bit ;

Phase\_1, Phase\_2 : out bit );

end entity 2\_Phase\_Clock ;

#### Assertion & Report Statements

Assertion Statements Check Expected Conditions at Their Location in the Program.

Assertion Statements Are Not "If" Statements Since They Test for the Correct, Expected Results Rather Than an Error.

#### Assertion & Report Statements

If Other Than the Expected Condition, the Report and Severity Expressions Are Executed

assertion\_label : ] assert Boolean\_expression

[ report expression ]

[ severity expression ] ;

#### **Assertion Statements**

Expression Must Evaluate to String

Uses in simulation

Notify user when statement is executed

Optionally print report expression

Optionally print severity (*e.g.*, note, warning, error, failure)

Determine whether to continue

# Report Statement

- A Note Is Printed Whenever the Expression Occurs

- Report Always Produces a Message Useful for Tracing Values or Paths During Execution

- Expression Must Evaluate to String

[ report\_label : ] report expression

[ severity expression ] ;

#### **Operator Precedence**

Highest to Lowest Unary operator: NOT Relational operators: =, /=, <, <=, >, >=Boolean (bitwise): AND, OR, NAND, NOR, XOR, XNOR Parentheses Can Be Used to Force particular order of evaluation Improve readability of expressions

# Type Declaration/Definition

type identifier is type\_definition ;

type\_definition <=

scalar\_type\_definition

composite\_type\_definition

access\_type\_definition

file\_type\_definition</pre>

# Scalar Type

scalar\_type\_definition <=

enumeration\_type\_definition

integer\_type\_definition

floating\_type\_definition

physical\_type\_definition</pre>

#### **Predefined Enumerated Types**

type severity\_level is ( note, warning, error, failure );

type Boolean is ( false, true );

Used to model abstract conditions

**type** bit **is** ( '0', '1' ); Used to model hardware logic levels

### Bit-Vector Type

Useful Composite Type Since It Groups Bits Together Which Can Represent Register Contents or Binary Numbers.

signal Out\_Port\_Adx: Bit\_Vector

( 15 downto 0 );

# Specifying Values with String Literal

Out\_Port\_Adx <= B "0110\_1001";

Out\_Port\_Adx <= X "69" ;</pre>

Out\_Port\_Adx <= 0 "151" ;

# Subtype (Slice)

Subtype: Values which may be Taken on by an Object are a Subset of some Base Type and may Include All Values.

subtype identifier is subtype\_indication ;

subtype\_indication <=

name [ range simple\_expression

( to | downto ) simple\_expression ]</pre>

# Other Subtypes

A Subtype may Constrain Values from a Scalar Type to be Within a Specified Range

subtype pin\_count is integer range 0 to

400 ;

subtype octal\_digits is character range

'0' to '7';

## Subtype Bounds

A Subtype May Constrain an Otherwise Unconstrained Array Type by Specifying Bounds for the Indices

subtype id is string (1 to 20); subtype MyBus is bit\_vector (8 downto 0);

# Attributes

#### Predefined Attributes Associated with Each Type

Type\_Name ` Attribute\_Name

#### Scalar Type Attributes

T'left leftmost value in T T'right rightmost value in T T'low least value in T T'high greatest value in T True if ascending range, T'ascending else false T'image(x) a string representing x T'value(s) the value in T that is represented by s

# **Discrete and Physical Attributes**

T' pos(x)position number of x in T value in T at position n T'val(n) T'succ(x)value in T at position one greater than that of x T'pred(x) value in T at position one less than that of x T'leftof(x) value in T at position one to the left of x T'rightof(x) value in T at position one to the right of x

# End of Lecture

Concurrent

Sequential

Conditional

Types

Attributes