## Modeling Constructs

1

#### Prof. K. J. Hintz

#### Department of Electrical and Computer Engineering George Mason University

# Modeling Constructs

- An Entity Declaration

- Describes the external interface (I/O signals)

- Multiple Architecture Bodies

- Describe alternative implementations of an entity

- » Increasing levels of fidelity to physical reality

- » Allows simulation to different degrees of detail

- Hierarchical Approach to Model Building

# Entity Declarations

#### Entities are the Primary Hardware Abstraction in VHDL and May Represent

- Entire system

- Subsystem

- Board

- Chip

- macro-cell

- logic gate

#### May Be Used Directly as a Component in a Design

**Entity Declarations**

#### May Be the Top Level Module of the Design

- Reside in library

- Usable by other designs

May Have No Port Clause When Used As a Test Bench Since All Signals Are Generated Internally

# Entity Declaration Syntax

entity identifier is

[ port ( port\_interface\_list ) ; ]

{ entity\_declarative\_item }

end [ entity ] [ identifier ] ;

# Interface List Syntax

port\_interface\_list <=

( identifier { , . . . } : [ mode ]

subtype\_indication [ := expression ] )

{ ; . . . }</pre>

mode <=

in | out | inout | buffer | linkage</pre>

Channels for Dynamic Communication Between a Block and Its Environment

#### Optional

– Not needed for testbench entities, *e.g.*,

entity TestNiCadCharger is

end entity TestNiCadCharger ;

#### Purpose Is to Define Interface

#### -in

» in only

#### - out

» out only

#### - inout

» Can be connected to multiple signals» Requires bus resolution function

#### – buffer

#### » Signal driving buffer drives output

- *i.e.*, no need to resolve

- » Signal driving buffer can also drive other internal signals

- *i.e.*, there is an implied buffer isolating internal usage from port signal

#### – linkage

» Means for connecting to foreign design entities, *e.g.*, Verilog

- Can Be Given Default Value Which Can Be Overridden When Instantiated

- Unconnected or unassociated signals of mode

in must have default expression

#### Port Clause, *e.g.*,

####

# Component vs Entity

- Entities Represent Real Devices Which Have Architectures to Implement Them

- Components Represent Interfaces to Entities or Virtual Devices

- Need to be declared

- » may be instantiated at same time

- » can be used to build structural model, instantiated later

# Component Declaration

- Declares a Virtual Design Entity Interface

- May Be Used to Associate a Component Instance With a Design Entity in a Library by Using

- Component configuration

- Configuration specification

### Component Declaration Syntax

#### component identifier [ is ]

- [ generic\_clause ]

- [ port\_clause ]

#### end component [ identifier ] ;

#### generic\_clause <= generic\_interface\_list );</pre>

## Component Declaration, *e.g.*

component mux\_2\_to\_1 is

generic ( tpd : time );

port ( in\_1, in\_2, mux\_out );

end component mux ;

## Component Instantiation Syntax

Identifier: [ component ]

component\_identifier

- [ generic map ( generic\_association\_list )]

- [ port map ( port\_association\_list ) ];

#### **Direct Component Instantiation**

Identifier: entity

entity\_identifier

- [ ( architecture\_identifier ) ]

- [ port map ( port\_association\_list ) ] ;

# Direct Component Instantiation, e.g.

And2\_1: entity

And2

- [ ( TI74LS00 ) ]

- [ port map ( pin2 => in\_1,

- $pin3 => in_2,$

- pin1 => out ) ] ;

# Configuration Declaration

- Declares Virtual Design Entity That May Be Used for Component Instantiation

- Components Need Not Be Bound When Declared, but Specified in Configuration

- Binds a Component Instance With a Design Entity in a Library

#### Basic Configuration Syntax

#### configuration identifier of entity\_name is

{ configuration\_declarative\_item }

block\_configuration

end [ configuration ] [ identifier ] ;

where identifier is the entity at the top of the design hierarchy

### Configuration Declarative Syntax

configuration\_declarative\_item <=

use\_clause

attribute\_specification

group\_declaration</pre>

#### (a *group\_declaration* declares a named collection of named entities)

# Block Configuration Syntax

#### A Block Is an Identified Group of Concurrent Statements

block\_configuration <=</pre>

for block\_specification

{ use\_clause }

{ configuration\_item }

end for ;

# Block Specification Syntax

#### block\_specification <=</pre>

architecture\_name

- block\_statement\_label

- generate\_statement\_label

- [ ( index\_specification ) ]

# Configuration Item Syntax

*configuration\_item* <=

block\_configuration

component\_configuration

Component Configuration Syntax Associates Binding Information With Component Labels

for component\_specification

[ binding\_indication ]

[ block\_configuration ]

end for ;

# Binding Indication

binding\_indication <=</pre>

- [ use entity\_aspect ]

- [ generic\_map\_aspect ]

- [ port\_map\_aspect ]

# Entities/Components

- Entities Can Be Defined Locally or in a Library

- Components Are Local Linkages to Entities in Libraries

Either Can Be Used in an Architecture, but Component Is More General and Allows for Reuse of Entities

# Architecture Bodies

- There May Be Multiple Architecture Bodies of the Same Entity With Each Architecture Body Describing a Different Implementation of the Entity.

- Behavior using the sequential or concurrent statements

- Structure of the entity as a hierarchy of entities

# Architecture Bodies

- Declarations Define Items That Will Be Used to Construct the Design Description.

- Signals used to connect submodules in a design

- Component port declarations are signals within the entity

# Architecture Body Syntax

architecture identifier of entity\_name is

{ block\_declarative\_item }

begin

{ concurrent\_statement }

end [ architecture ] [ identifier ] ;

# Concurrent Statements

#### No Temporal Ordering Among the Statements

A Signal Assignment Statement Is a Sequential Statement and Can Only Appear Within a Process.

# Concurrent Statements

- A Process of Sequential Statements Behaves As If It Were One Concurrent Statement

- Internally sequential

- Externally concurrent

## Signal Declarations

#### Signals Can Be Declared Internal to an Architecture to Connect Entities

Variables Are Not Appropriate Since They Do Not Have the Temporal Characteristics of Hardware

# Signal Declarations

Signals Declared Within an Entity Are Not Available Unless Specified in the Port Clause of the Entity Declaration.

#### Discrete Event Simulation

– Signal changes are scheduled in the future

#### Signal Syntax

signal identifier { , . . . } :

subtype\_indication [ := expression ] ;

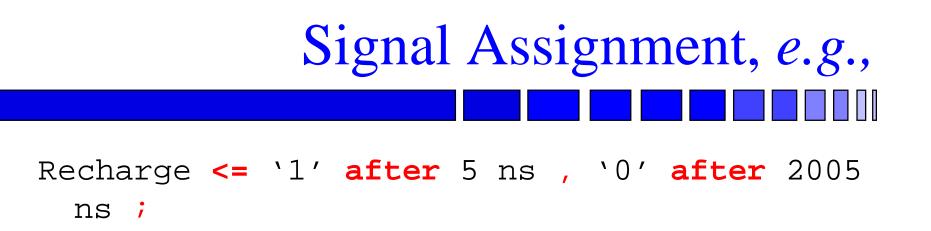

[ label : ] name <= [ delay\_mechanism ]

waveform ;</pre>

#### Waveform Syntax

waveform <=</pre>

( value\_expression [ after time\_expression ] )

{ , . . }

- Executes in Zero Time

- Schedules Future Event

- Time References Are Relative to Current Time

- *Recharge* returns to zero 2 ms after it goes high, not 2.005 ms after it goes high

### **Discrete Event Simulation**

- Transaction

- A scheduled change in a signal value

- Active Signal

- A simulation cycle during which a signal transaction occurs

- Event

A transaction which results in a signal's value changing

### Given a signal, S, and a value T of type time

**Signal Attributes**

S'delayed (T) A signal that takes on the same values as S but is delayed by time T

S'stable (T) A Boolean signal that is true if there has been no event on S in the time interval T up to the current time, else false

S'quiet (T) A Boolean signal that is true if there has been no transaction on S in the time interval T up to the current time, else false

### Signal Attributes

- S'transactionA signal of type bit that changes value<br/>from '0' to '1' or vice versa each time there<br/>is a transaction on SS'eventTrue if there is an event on S in the current

- simulation cycle, else false S'active True if there is a transaction on S in the

- current simulation cycle, else false

- **S'last\_event** The time interval since the last event on **S**

**S'last\_active** The time interval since the last trans. on **S**

S'last\_value Value of S just before the last event on S

# Signal Attributes, *e.g.*, 1\*

if clk'event and ( clk = '1' or clk = 'H' ) and ( clk'last\_value = `0' or clk'last\_value = `L') then **assert** d'last\_event >= Tsu report "Timing error: d changed within setup time of clk" ; end if ;

#### Signal Attributes, e.g., 2\* entity edge\_triggered\_Dff is port ( D, clk, clr : in bit ; $\bigcirc$ : out bit ) end entity edge\_triggered\_Dff ; **architecture** behavioral **of** edge triggered Dff is begin state\_change : process (clk, clr) is

# Signal Attributes Example 2\*

#### begin if clr = `1' then Q <= `0' after 2 ns ; elsif clk'event and clk = '1' then Q <= D after 2 ns ; end if ; end process state\_change ; end architecture behavioral ;

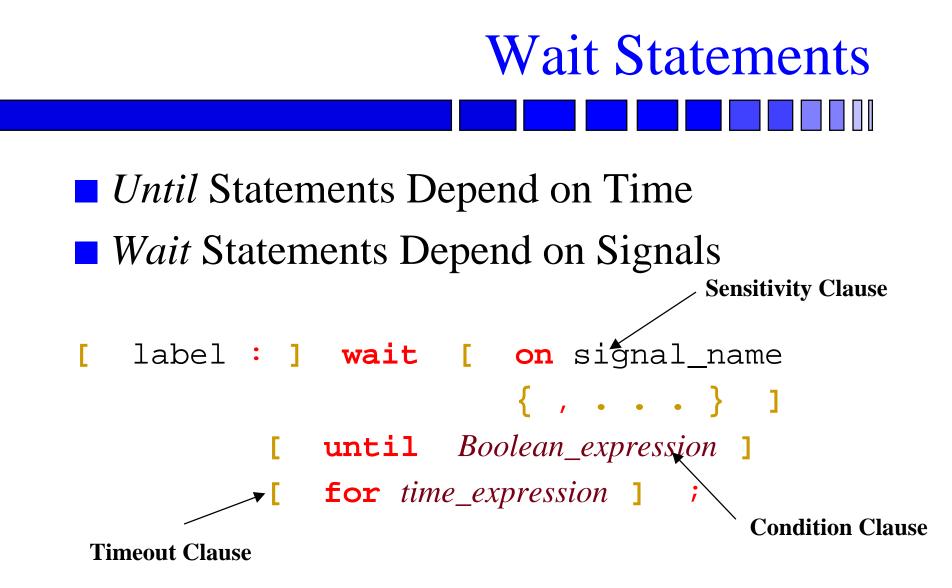

## Wait Statements

#### All Clauses Are Optional

#### Wait Statements Are The Only Ones That Take More Than Zero Time to Execute

#### Simulation Time Only Advances With Wait Statements

Wait Statements

- A Process Without a Wait Statement Is an Infinite Loop.

- Processes with sensitivity lists have an implied wait statement at the end of the process.

- A process must have either a wait statement or a sensitivity list.

## Sensitivity Clause

#### Sensitivity Clause

- A list of signals to which the process responds

- An event (change in value) on any signal causes the process to resume

- Shorthand--sensitivity list in heading rather than wait statement at end of process.

### process (clk, clr) is begin

end ;

process is

begin

wait on clk, clr ;

end ;

# Condition Clause

- When Condition Is True, Process Resumes

- Condition Is Tested Only While the Process Is Suspended

- Even if the condition is true when the wait is executed, the process will suspend

- In order to test the condition,

- » A signal in the sensitivity list must change, or,

- » *IFF* there is no sensitivity list, an event must occur on a signal within the condition

# Timeout Clause

## Specifies the Maximum Simulation Time to Wait.

#### • A Sensitivity or Condition Clause May Cause the Process to Resume Earlier.

# Concurrent Signal Assignments

Functional Modeling Implements Simple Combinational Logic.

- Concurrent Signal Assignment Statements Are an Abbreviated Form of Processes

- Conditional signal assignment statements

- Selected Signal Assignment Statements

#### Shorthand *if* Statement

#### Sensitive to ALL Signals Mentioned in Waveforms and Conditions.

## Conditional Signal Assignment Syntax

[ label : ] name <= [ delay\_mechanism ]

{ waveform when Boolean\_expression else }

waveform [ when Boolean\_expression ] ;</pre>

# unaffected

- Can make *Waveform* Not Schedule a Transaction on the Signal in Response to an Event using unaffected

- Can Only Be Used in Concurrent Signal Assignment Statements

- when not priority\_waiting and

server\_status = ready else unaffected ;

#### Shorthand for **case** Statement

#### All Rules of **case** Statement Apply

#### **unaffected** Also Applies

# Selected Signal Assignments

[ label : ] with expression select

name <= [ delay\_mechanism ]

{ waveform when choices , }

waveform when choices ;</pre>

## Concurrent Assertions

- Shorthand for Process With a Sequential Assertion Statement

- Checks *Boolean\_expression* Each Time Signal Mentioned in It Changes

- [ label : ] assert Boolean\_expression

- report expression ]

- severity expression ] ;

# Concurrent Assertions

Compact Manner for Including Timing and Correctness Checks in Behavioral Models

– *e.g.*, for S-R flip flop

assert not ( s = `1' and r = `1' )

report "Illegal inputs";

### **Entity and Passive Processes**

entity identifier is

- [ port ( port\_interface\_list ) ; ]

- { entity\_declarative\_item }

[ begin

concurrent\_assertion\_statement

passive\_concurrent\_procedure\_call\_statement

passive\_process\_statement } ]

end [ entity ] [ identifier ] ;

## Passive Statements

Statements Are Passive If They Do Not Affect the Operation of the Entity in Any Way.

Concurrent Assertion Statements Are Passive Since They Only Test Conditions

#### A Process Statement Is Passive If It Does NOT Contain

**Passive Statements**

- any signal assignments, or

- calls to procedures containing signal assignment statements

- Concurrent Procedure Call Statements

- not yet covered

# Passive Statement Example\*

- entity S\_R\_flipflop is

- port ( s , r : in bit ;

- q , q\_n : out bit ) ;

#### begin

- check: assert not ( s = 1' and r = 1' )

- report "Incorrect use of S\_R\_flip\_flop: s

and r both `1'";

end entity S\_R\_flipflop ;

# End of Lecture