- >Variable

assignment

statement

- >Signal assignment

- >wait

## Sequential Statements

- ➤ Variable assignment statement

- ➤ Signal assignment

- **➤** If statement

- ➤ Case statement

- **➤** Loop statement

- > Next statement

- > Exit statement

- ➤ Null statement

- > Procedure call statement

- > Return statement

- ➤ Assertion statement

# Variable assignment statement

<u>Variable\_assignment\_statement</u> ::= target:=expression;

```

architecture RTL of VASSIGN is

signal A, B, J: bit_vector(1 downto 0);

signal E, F, G: bit;

begin

p0 : process (A, B, E, F, G, J)

variable C, D, H, Y : bit_vector(1 downto 0);

variable W, Q : bit_vector(3 downto 0);

: bit_vector(0 to 7);

variable Z

variable X : bit;

variable DATA : bit_vector(31 downto 0);

begin ...

end process

end RTL;

```

### Variable assignment statement

```

signal A, B, J : bit_vector(1 downto 0);

signal E, F, G : bit;

> p0 : process (A, B, E, F, G, J)

> -- A, B, J, D, H : bit_vector

-- E, F, G : bit

Variable assigned to a signal

> C := "01";

X := E nand F;

Y := H or J;

The same signal

C (1 i)

```

The same signal G (a bit) goes to two bits

```

D := ('1', '0');

W := (2 downto 1 => G, 3 => '1', others => '0');

DATA := (others => '0');

end process;

```

Z(0 to 3) := C & D;

Z(4 to 7) := (not A) & (A nor B);

Make note of mapping notation again

# Formal Syntax of a signal assignment statement

VHDL syntax description in metalanguage

```

Signal assignment statement ::=

```

```

target<=[transport]waveform_element{,waveform_element};</pre>

```

waveform\_element::=

value\_expression[after time\_expression]|null[after time\_expression]

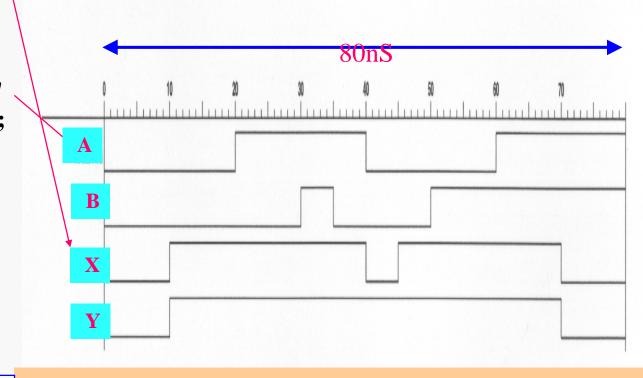

X <= transport A nand B

after 10 ns;

end process;

p1 : process

begin

A <= '0', '1' after 20 ns, '0'

after 40 ns, '1' after 60 ns;

B <= '0', '1' after 30 ns, '0'

after 35 ns, '1' after 50 ns;

wait for 80 ns;

end process;

Y <= A nand B after 10 ns;

p0: process (A, B)

begin

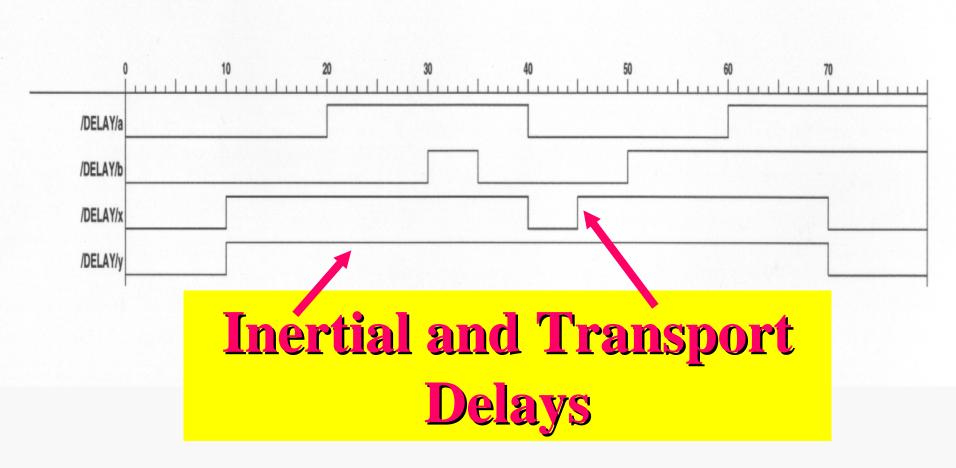

## Signal assignment statements and wait for

A pulse with a duration shorter than the switching time of the circuit will not be transmitted in **transport**.

Recall waveforms, transport and inertial delay

## Signal assignment statement

```

entity DELAY is

p1: process

end DELAY;

begin

A <= '0', '1' after 20 ns,

architecture RTL of DELAY is

'0' after 40 ns, '1' after 60 ns;

signal A, B, X, Y: bit;

begin

B <= '0', '1' after 30 ns,

p0: process (A, B)

'0' after 35 ns, '1' after 50 ns;

begin

wait for 80 ns;

Y <= A nand B after 10 ns;

end process;

X <= transport A nand B after

end RTL;

10 ns:

end process;

/DELAY/a

/DELAY/b

/DELAY/x

/DELAY/y

```

FIGURE 4.1 Inertial and transport delay.

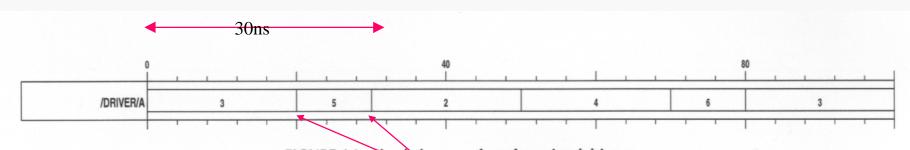

### Role of wait for in discarding

FIGURE 4.2 Simulation waveform for a signal driver.

```

entity DRIVER is

end DRIVER;

architecture RTL of DRIVER is

signal A: integer;

begin

pa: process

begin

```

```

A <= 3, 5 after 20 ns, 7 after 40 ns, 9 after 60 ns; wait for 30 ns;

A <= 2, 4 after 20 ns, 6 after 40 ns, 8 after 60 ns; wait for 50 ns; end process; end RTL;

```

This slide explains the role of **wait for** to discard part of assignment statement

## Differences between variables and signals

#### ➤ 1. Where declared

- ➤ Local variables are declared and only visible <u>inside a</u> <u>process</u> or a subprogram.

- ➤ **Signals** cannot be declared inside a process or a subprogram.

#### > 2. When updated

- ➤ A **local variable** is <u>immediately updated</u> when the variable assignment statement is executed.

- ➤ A **signal** assignment statement <u>updates the signal</u> <u>driver</u>. The new value of the signal is <u>updated when the process is suspended.</u>

## Differences between variables and signals

- 3. Variables are cheaper to implement in VHDL simulation since the evaluation of drivers is not needed. They require less memory.

- 4. Signals communicate among concurrent statements. Ports declared in the entity are signals. Subprogram arguments can be signals or variables.

- 5. A signal is used to indicate an interconnect (net in a schematic). A local variable is used as a temporary value in a function description.

## Signals versus variables

6. A local variable is very useful to factor out common parts of complex equations to reduce the mathematical calculation.

#### 7. Right-hand sides:

- ➤ The right-hand side of a <u>variable assignment</u> statement is an <u>expression</u>.

- > There is no associated time expression.

- ➤ The right-hand side of a signal assignment statement is a sequence of waveform elements with associated time expressions.

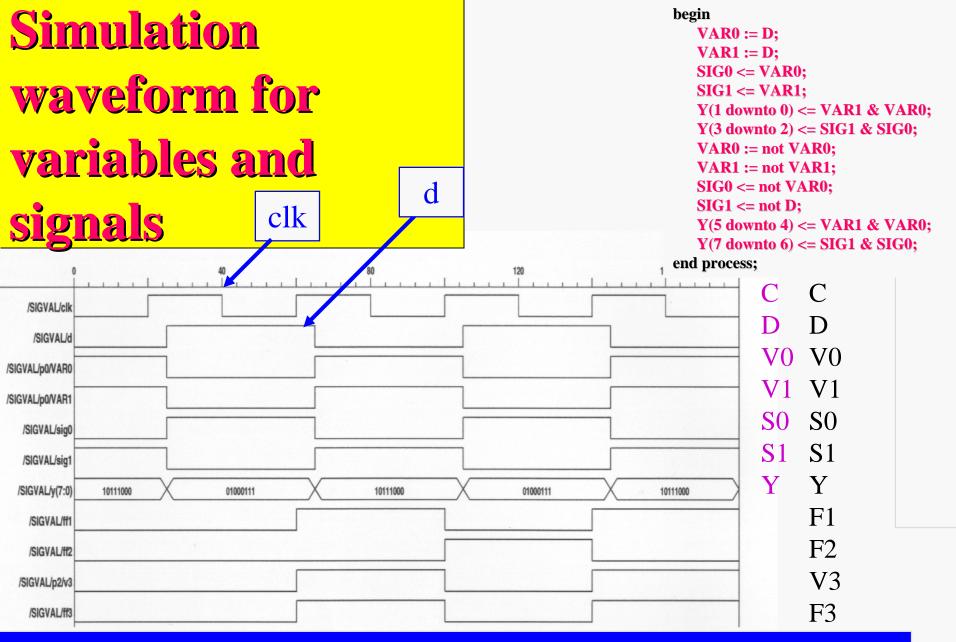

# Signals and variables in timing diagrams

```

Variables on left

begin

entity SIGVAL is

VAR0 := D;

Variables on

port (

VAR1 := D;

right

CLK, D: in bit;

SIG0 <= VAR0;

FF2, FF3: out bit;

SIG1 \leftarrow VAR1;

Y(1 downto 0) <= VAR1 & VAR0;

Y : out bit_vector(7 downto 0));

Y(3 downto 2) <= SIG1 & SIG0;

end SIGVAL;

VAR0 := not VAR0;

architecture RTL of SIGVAL is

VAR1 := not VAR1;

signal FF1, SIG0, SIG1 : bit;

SIG0 \le not VAR0;

begin

SIG1 \le not D;

p0: process (D, SIG1, SIG0)

Y(5 downto 4) <= VAR1 & VAR0;

Y(7 downto 6) <= SIG1 & SIG0;

variable VAR0, VAR1: bit;

end process;

```

# Timing of variables versus FF2 is old value of FF1 according to signal semantics timing of signals

p1: process begin CLK /SIGVAL/clk wait until CLK'event and CLK = '1'; SIGVALIC VAR0 FF1 <= D; FF2 <= FF1; /SIGVAL/po/VARO VAR1 /SIGVAL/powart SIG0 end process; /SIGVAL/sig( SIG1 p2: process /SIGVAL/sig1 variable V3: bit; /SIGVAL/v(7:0) SIGVALIFI begin FF1 /SIGVAL/ff2 wait until CLK'event and CLK = '1'; FF2 SIGVAL/p2/v3 V3 V3 := D; FF3 <= V3;/SIGVAL/ff3 FF3 end process; •Variable V3 changes at the same time as FF1, and so FF3

• FF3 unlike FF2

end RTL;

\_\_\_\_ MORAL: Signals are scheduled, variables change immediately

## **Three** architectures

```

entity TEMP is

end TEMP:

architecture RTL of TEMP is

signal A, B, C, D, E, F, G, Y, Z: integer;

begin

p0: process (A, B, C, D, E, F, G)

begin

Y \le A + (B*C + D*E*F + G);

Z \le A - (B*C + D*E*F + G);

end process;

end RTL;

architecture RTL1 of TEMP is

signal A, B, C, D, E, F, G, Y, Z: integer;

begin

```

**p0** : **process** (A, B, C, D, E, F, G)

```

variable V: integer:

v calculated

immediately

begin

V := (B*C + D*E*F + G);

Y \le A + V; Z \le A - V;

The same

end process;

statements

end RTL1;

architecture RTL2 of TEMP is

signal A, B, C, D, E, F, G, Y, Z: integer;

signal V: integer;

begin

p0: process (A, B, C, D, E, F, G)

begin

V \le (B*C + D*E*F + G);

Y \le A + V; Z \le A - V;

Uses old value

of v, because it

end process;

is a signal

end RTL2;

```

First architecture has no variables

Second architecture uses variable V

Third architecture uses additional signal V

Their operation is different because signal V is scheduled and variable immediately assigned

### Sources

➤ VLSI. Ohio University, Starzyk